순차회로

클럭 펄스 : 동기화를 위해 클럭 발생기라는 장치를 통해 주기적으로 이루어지는 신호

- 레벨 : High(1) Low(0)인 상태

- 트리거 신호 : 레벨을 High 또는 Low로 변화하게 만드는 신호

- 엣지 : 0 -> 1(Positive-edge), 1->0(Negative-edge) 으로 변화하는 상태

- 래치는 레벨에 반응 (입력에 클럭이 없다?? 그럼 래치)

- 플리플롭은 엣지에 반응

SR 래치 : 두개의 상호 결합된 NOR 게이트 또는 NAND 게이트로 구성된 회로. 리셋(R)과 세트(S)의 입력을 가짐

NOR 게이트로 구성된 SR 래치

세트 상태 (Q = 1, Q' = 0), 리셋 상태 (Q = 0, Q' = 1)

(1, 1)입력은 금지됨

NAND 게이트로 구성된 SR 래치(S'R' 래치라고 간주하기도 함)

NOR 구성 SR래치와 보수형태

(0, 0) 입력은 금지 됨

제어 입력을 가진 SR 래치

En 입력이 LOW면 변화 없음(이전 상태 유지)

NOR 포함 로직이면 위부터 R En S 순 입력, ,

NAND 포함 로직이면 위부터 S En R 순 입력, ,

En 없는 로직과 반대되는 값을 출력함

D 래치(투과형 래치, Data latch)

NAND en latch 로직에 입력이 D로 바뀌어있는 형태

D와 En입력이 있고 En이 high 일 경우에만 Q를 D로 출력

En low면 유지

플리플롭 : 레벨이 아닌 엣지를 입력값으로 사용하는 로직

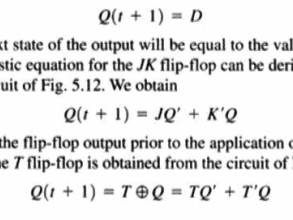

D 플리플롭 : 상향 엣지가 감지될 때 직전 상태의 D 값을 출력해주는 로직

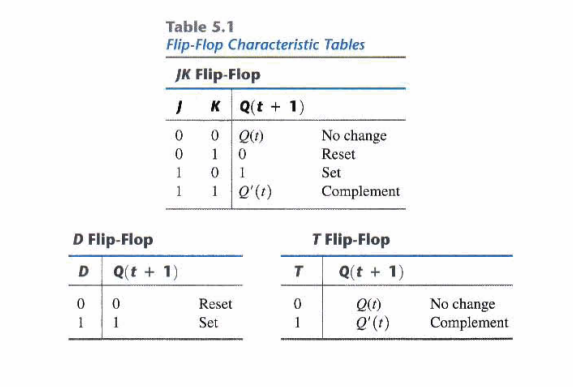

JK 플리플롭 : 유지와 토글 기능도 포함하는 플리플롭 (J는 S, K는 R에 대응, 11입력시 토글)

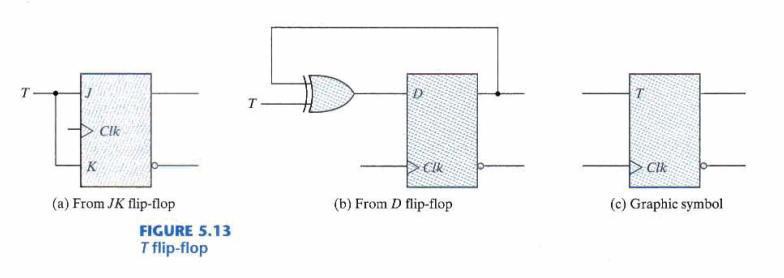

T 플리플롭 : T값에 따라 출력을 Toggle 시키는 플리플롭

특성표, 특성식

Q(t) : 현재 상태 (clock edge 적용 이전 상태)

Q(t+1) : 다음 상태(천이 적용 후 상태)

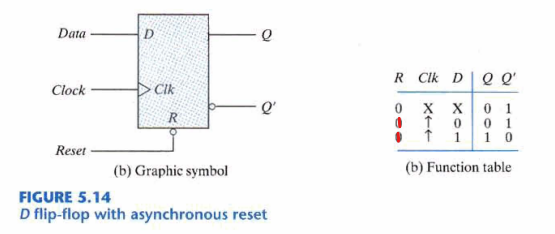

직접 입력

직접 리셋 ,직접 세트를 위한 입력

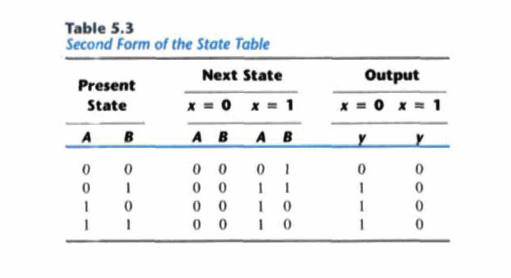

클럭형 순사회로 해석

회로도 -> 방정식 -> 상태표 -> 상태도

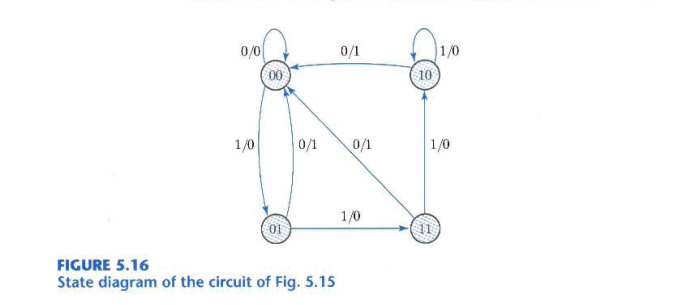

상태도

노드 : 현재 상태, 다음 상태

엣지 : 입출력

유한 상태 머신(FSM, finite state machine)

밀리(Mealy) 모델 : 현재 상태와 입력에 의존

무어(Moore) 모델 : 현재 상태에만 의존

FSM 속 엣지 : 두 상태 사이 천이(transition)를 의미

상태 축소

두 개의 현재 상태에 대해 다음 상태와 입출력이 같은 경우 하나 삭제 가능

상태 할당

상태에 이진코드를 할당하는 과정

2진수, 그레이 코드, 원핫

뒤로 갈 수록 플립플롭은 늘어나지만 논리식이 간단해져서 비교해보고 설계해야 됨

레지스터

데이터 레지스터 : 병렬

시프트 레지스터 : 직렬, 왼쪽에서 오른쪽으로

'CS > 논리 회로' 카테고리의 다른 글

| [논리 회로] 게이트 레벨 최소화 (0) | 2023.03.25 |

|---|